April 2022

## High Density 16Rx / 8Tx or 8Rx / 4Tx ARINC 429 Protocol IC with optional Integrated Line Receivers

### **GENERAL DESCRIPTION**

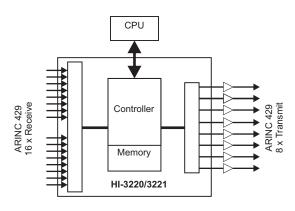

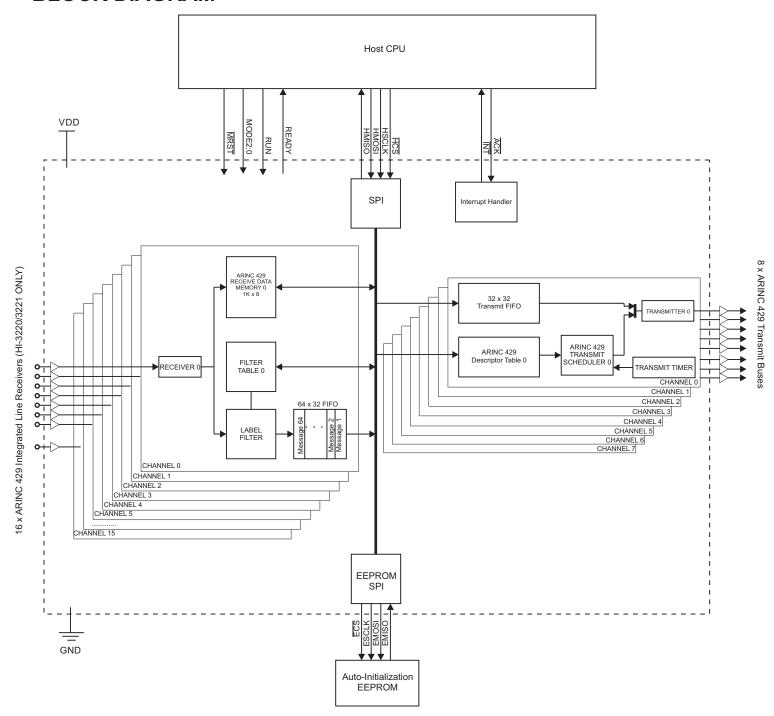

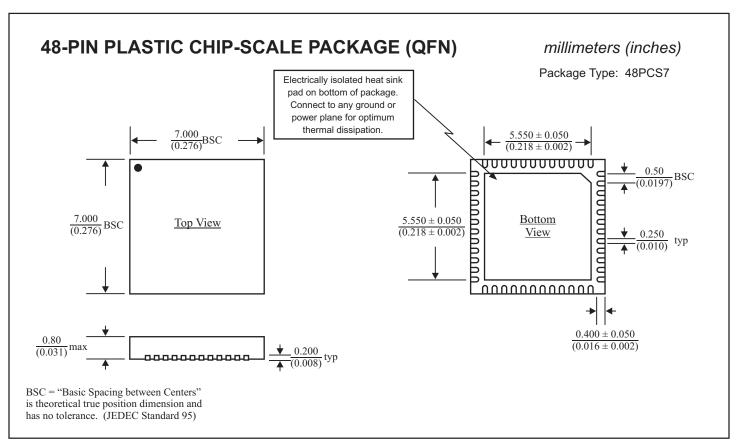

The HI-3220 from Holt Integrated Circuits is a family of single chip CMOS high density application data management ICs capable of managing, storing and forwarding avionics data messages between sixteen ARINC 429 receive channels and eight ARINC 429 transmit channels. Options for eight receive and four transmit channels are also available in a compact, cost effective 7mm x 7mm QFN package footprint.

The ARINC 429 buses may operate independently - the IC can be programmed to automatically re-format, re-label, re-packetize and re-transmit data from ARINC 429 receive buses to ARINC 429 transmit buses. Alternatively, a host CPU can send and receive data on multiple buses. 32KB of on-board memory allows received data to be logically organized and automatically updated as new ARINC 429 labels are received via ARINC 429 label mailboxes. A 64 message deep Receive FIFO is also available for each receive channel. Each transmitter has the option to independently enable a programmable scheduler on the ARINC 429 bus, or to have the CPU directly send data. An optional auto-initialization feature allows configuration information to be up-loaded from an external EEPROM on reset to facilitate rapid start-up or operation without a host CPU.

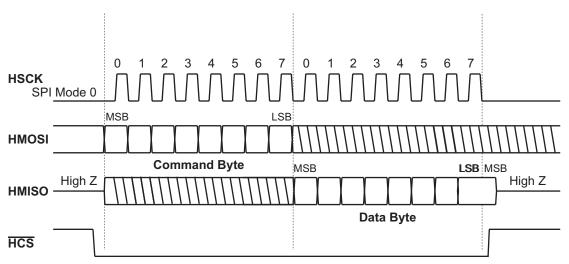

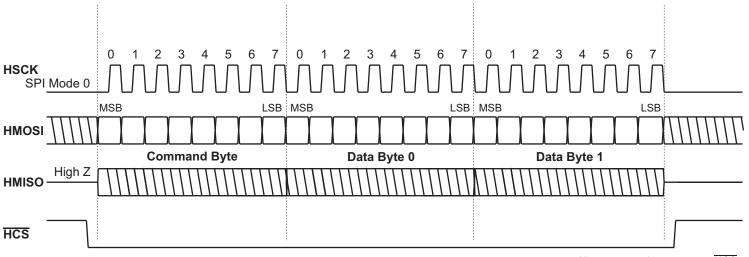

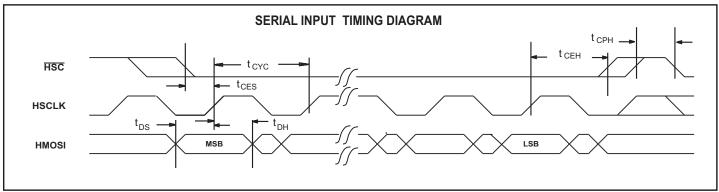

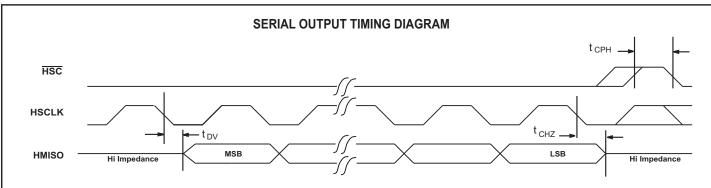

The HI-3220, HI-3221, HI-3222 and HI-3223 have integrated ARINC 429 line receivers, capable of RTCA/DO-160 level 3 lightning compliance with external  $40k\Omega$  resistors. HI-3225 and HI-3226 utilize external line receivers, for example Holt's octal HI-8458 family. The HI-3222 and HI-3223 are 8-channel receive, 4-channel transmit options available in smaller package footprints, with HI-3223 having the same slope control feature as HI-3220. Transmit outputs interface directly to external HI-8592, HI-8596, or integrated lightning protected HI-8597 ARINC 429 line drivers. All parts use a 40 MHz 4-wire SPI (Serial Peripheral Interface) host connection.

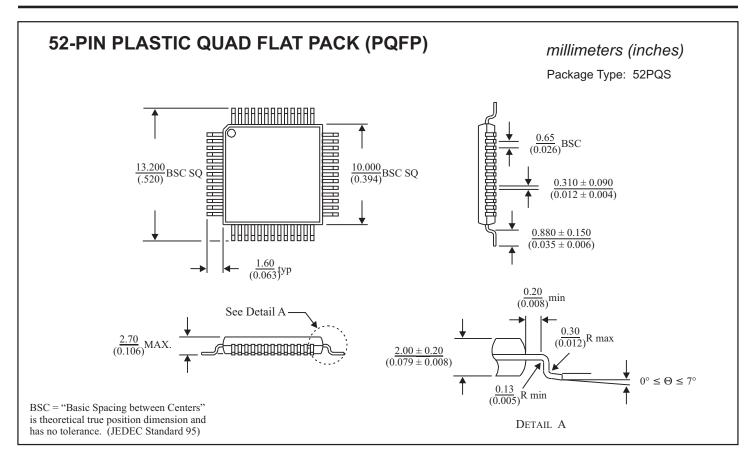

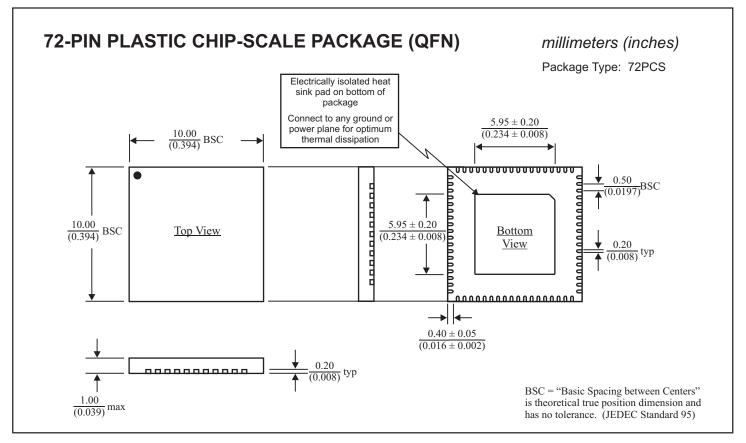

HI-3220 and HI-3225 are available in an 80-pin PQFP package, whereas HI-3221 and HI-3226 are available in a 72-pin 10mm x 10mm QFN package. The HI-3222 (8-ch. Rx, 4-ch. Tx) is available in a very compact 48-pin 7mm x 7mm QFN.

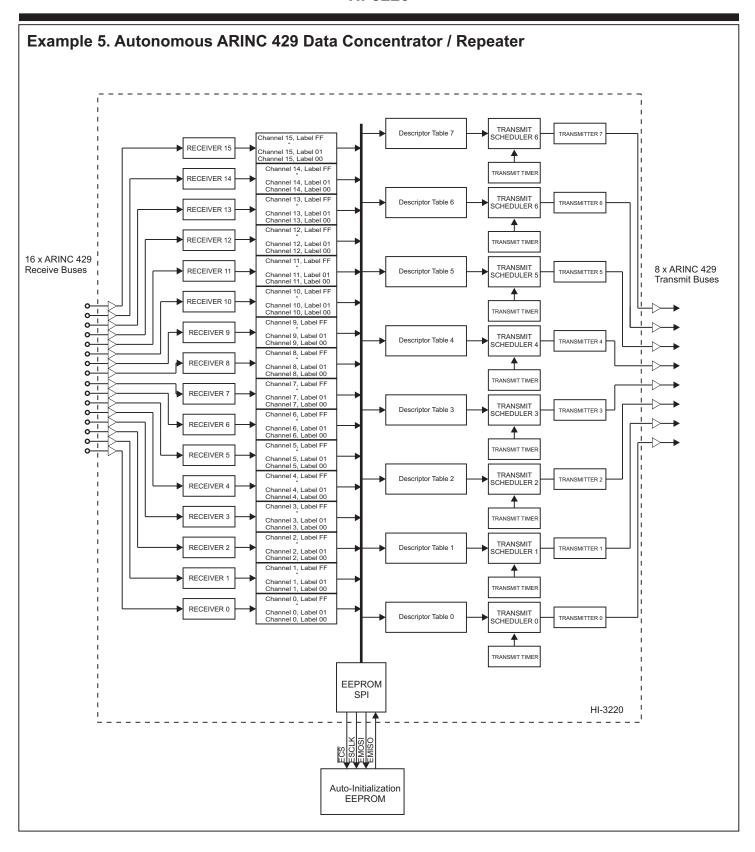

## **APPLICATION**

### **FEATURES**

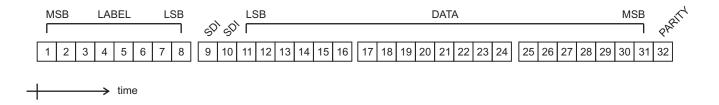

- Fully compliant to ARINC 429 Specification

- Sixteen ARINC 429 Receive channels with optional integrated line Receivers

- Eight ARINC 429 Transmit channels

- 8-channel Rx, 4-channel Tx version available in compact 48-pin 7mm x 7mm QFN

- 32 KB on chip user-configurable data storage memory

- Programmable receive data filtering

- Option for programmable transmission schedulers for periodic ARINC 429 broadcasting or CPU directed transmission

- Auto-initialization feature allows power-on configuration or independent operation without CPU

- 40 MHZ SPI CPU interface

- Transmitter rate and tri-state control outputs

- Supports 100kbs / 50kbs / 12.5kbs data rates

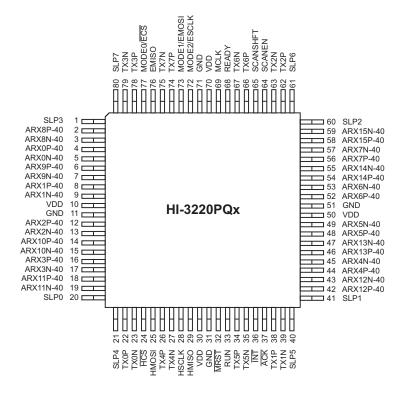

#### PIN CONFIGURATION

80 - Pin Plastic Quad Flat Pack (PQFP)

(DS3220 Rev. L) 04/22

## **BLOCK DIAGRAM**

## **PRODUCT OPTIONS**

| PART NUMBER | PACKAGE                  | LINE RECEIVERS | TRANSMIT CHANNELS                 |

|-------------|--------------------------|----------------|-----------------------------------|

| HI-3220     | 80-pin QFP               | 16 on-chip     | 8 Transmitters & SLP7:0 outputs   |

| HI-3221     | 72-pin QFN               | 16 on-chip     | 8 Transmitters. No SLP7:0 outputs |

| HI-3222     | 48-pin QFN               | 8 on-chip      | 4 Transmitters. No SLP outputs    |

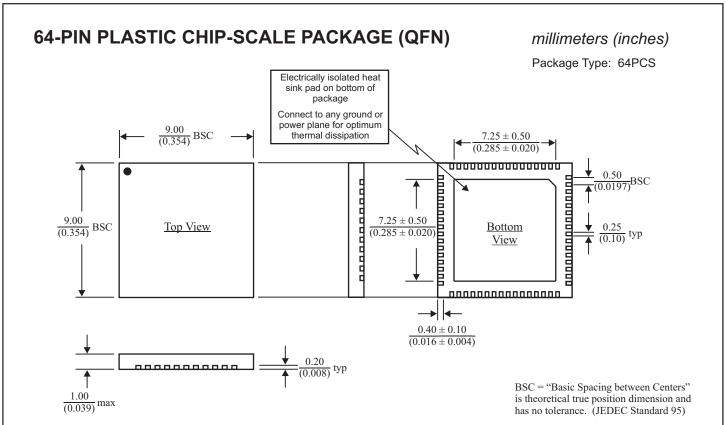

| HI-3223     | 52-pin QFP or 64-pin QFN | 8 on-chip      | 4 Transmitters & SLP3:0 outputs   |

| HI-3225     | 80-pin QFP               | 16 External    | 8 Transmitters & SLP7:0 outputs   |

| HI-3226     | 72-pin QFN               | 16 External    | 8 Transmitters. No SLP7:0 outputs |

## PIN DESCRIPTIONS (HI-3220, HI-3221, HI-3222, HI-3223)

| Signal       | Function     | Description                                                                                                            | Internal     |

|--------------|--------------|------------------------------------------------------------------------------------------------------------------------|--------------|

|              |              |                                                                                                                        | Pull-Up/Down |

| ACK          | INPUT        | Interrupt Acknowledge. Active low.                                                                                     | Pull-Up      |

| ĪNT          | OUTPUT       | Interrupt. Active low, open-drain.                                                                                     | Pull-Up      |

| ARX0N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 0. Requires external 40KOhm resistor.                            |              |

| ARX0P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 0. Requires external 40KOhm resistor.                            |              |

| ARX1N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 1. Requires external 40KOhm resistor.                            |              |

| ARX1P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 1. Requires external 40KOhm resistor.                            |              |

| ARX2N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 2. Requires external 40KOhm resistor.                            |              |

| ARX2P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 2. Requires external 40KOhm resistor.                            |              |

| ARX3N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 3. Requires external 40KOhm resistor.                            |              |

| ARX3P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 3. Requires external 40KOhm resistor.                            |              |

| ARX4N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 4. Requires external 40KOhm resistor.                            |              |

| ARX4P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 4. Requires external 40KOhm resistor.                            |              |

| ARX5N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 5. Requires external 40KOhm resistor.                            |              |

| ARX5P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 5. Requires external 40KOhm resistor.                            |              |

| ARX6N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 6. Requires external 40KOhm resistor.                            |              |

| ARX6P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 6. Requires external 40KOhm resistor.                            |              |

| ARX7N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 7. Requires external 40KOhm resistor.                            |              |

| ARX7P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 7. Requires external 40KOhm resistor.                            |              |

| ARX8N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 8. Requires external 40KOhm resistor.                            |              |

| ARX8P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 8. Requires external 40KOhm resistor.                            |              |

| ARX9N-40     | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 9. Requires external 40KOhm resistor.                            |              |

| ARX9P-40     | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 9. Requires external 40KOhm resistor.                            |              |

| ARX10N-40    | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 10. Requires external 40KOhm resistor.                           |              |

| ARX10P-40    | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 10. Requires external 40KOhm resistor.                           |              |

| ARX11N-40    | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 11. Requires external 40KOhm resistor.                           |              |

| ARX11P-40    | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 11. Requires external 40KOhm resistor.                           |              |

| ARX12N-40    | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 12. Requires external 40KOhm resistor.                           |              |

| ARX12P-40    | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 12. Requires external 40KOhm resistor.                           |              |

| ARX13N-40    | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 13. Requires external 40KOhm resistor.                           |              |

| ARX13P-40    | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 13. Requires external 40KOhm resistor.                           |              |

| ARX14N-40    | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 14. Requires external 40KOhm resistor.                           |              |

| ARX14P-40    | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 14. Requires external 40KOhm resistor.                           |              |

| ARX15N-40    | ANALOG INPUT | ARINC 429 Receive bus negative line input for channel 15. Requires external 40KOhm resistor.                           |              |

| ARX15P-40    | ANALOG INPUT | ARINC 429 Receive bus positive line input for channel 15. Requires external 40KOhm resistor.                           |              |

| TX0N         | OUTPUT       | ARINC 429 Tx channel 0 negative data output to line driver                                                             |              |

| TX0P         | OUTPUT       | ARINC 429 Tx channel 0 positive data output to line driver                                                             |              |

| TX1N         | OUTPUT       | ARINC 429 Tx channel 1 negative data output to line driver                                                             |              |

| TX1P         | OUTPUT       | ARINC 429 Tx channel 1 positive data output to line driver                                                             |              |

|              |              | ' '                                                                                                                    |              |

| TX2N<br>TX2P | OUTPUT       | ARINC 429 Tx channel 2 negative data output to line driver  ARINC 429 Tx channel 2 positive data output to line driver |              |

|              | OUTPUT       | ·                                                                                                                      |              |

| TX3N         |              | ARINC 429 Tx channel 3 negative data output to line driver                                                             |              |

| TX3P         | OUTPUT       | ARINC 429 Tx channel 3 positive data output to line driver                                                             |              |

| TX4N         | OUTPUT       | ARINC 429 Tx channel 4 negative data output to line driver                                                             |              |

| TX4P         | OUTPUT       | ARINC 429 Tx channel 4 positive data output to line driver                                                             |              |

| TX5N         | OUTPUT       | ARINC 429 Tx channel 5 negative data output to line driver                                                             |              |

| TX5P         | OUTPUT       | ARINC 429 Tx channel 5 positive data output to line driver                                                             |              |

| TX6N         | OUTPUT       | ARINC 429 Tx channel 6 positive data output to line driver                                                             |              |

| TX6P         | OUTPUT       | ARINC 429 Tx channel 6 positive data output to line driver                                                             |              |

| TX7N         | OUTPUT       | ARINC 429 Tx channel 7 positive data output to line driver                                                             |              |

| TX7P         | OUTPUT       | ARINC 429 Tx channel 7 positive data output to line driver                                                             |              |

| SLP0         | OUTPUT       | ARINC 429 Tx channel 0 slew rate control (see Tx Control Register) (HI-3220 and HI-3223).                              |              |

| SLP1         | OUTPUT       | ARINC 429 Tx channel 1 slew rate control (see Tx Control Register) (HI-3220 and HI-3223).                              |              |

| SLP2         | OUTPUT       | ARINC 429 Tx channel 2 slew rate control (see Tx Control Register) (HI-3220 and HI-3223).                              |              |

| SLP3         | OUTPUT       | ARINC 429 Tx channel 3 slew rate control (see Tx Control Register) (HI-3220 and HI-3223).                              |              |

| SLP4         | OUTPUT       | ARINC 429 Tx channel 4 slew rate control (see Tx Control Register) (HI-3220 and HI-3223).                              |              |

| SLP5         | OUTPUT       | ARINC 429 Tx channel 5 slew rate control (see Tx Control Register) (HI-3220 and HI-3223).                              |              |

| SLP6         | OUTPUT       | ARINC 429 Tx channel 6 slew rate control (see Tx Control Register) (HI-3220 and HI-3223).                              |              |

| SLP7         | OUTPUT       | ARINC 429 Tx channel 7 slew rate control (see Tx Control Register) (HI-3220 and HI-3223).                              |              |

## PIN DESCRIPTIONS (HI-3220, HI-3221, HI-3222, HI-3223) continued

| Signal      | Function | Description                                                                                   | Internal       |

|-------------|----------|-----------------------------------------------------------------------------------------------|----------------|

|             |          |                                                                                               | Pull-Up/Down   |

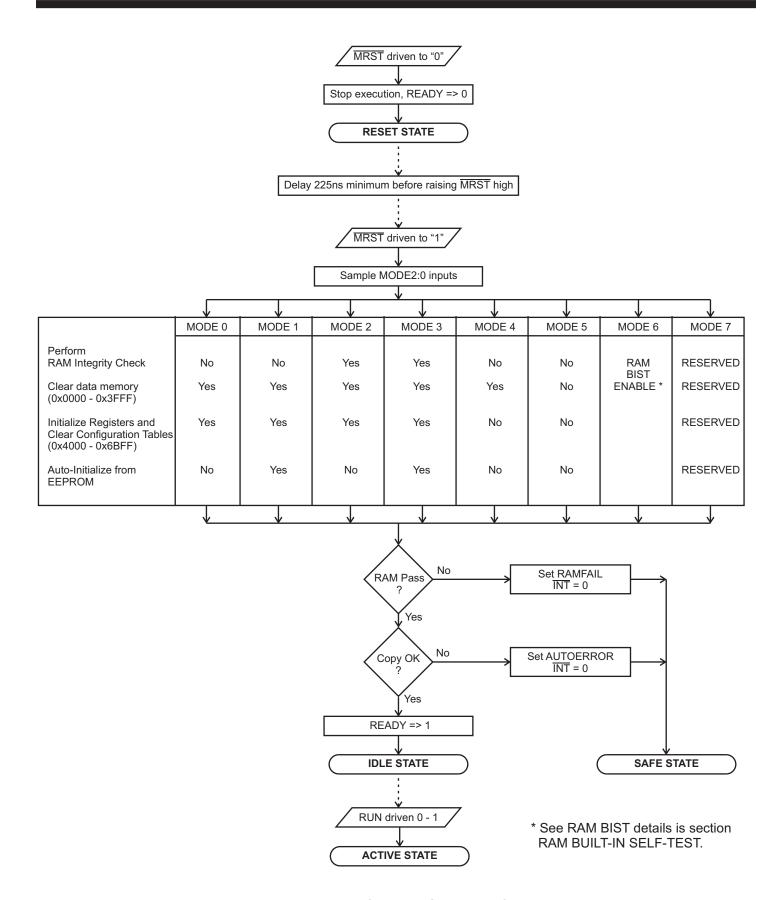

| MODE0/ECS   | I/O      | MODE0 configuration input sampled at reset / SPI chip select output for initialization EEPROM | See Note below |

| EMISO       | INPUT    | SPI serial data input from auto-inialization EEPROM                                           | Pull-Down      |

| MODE1/EMOSI | I/O      | MODE1 configuration input sampled at reset / SPI serial data output to initialization EEPROM  | See Note below |

| MODE2/ESCLK | I/O      | MODE2 configuration input sampled at reset / SPI clock for auto-initialization EEPROM         | See Note below |

| GND         | POWER    | Chip 0V supply. All four pins must be connected.                                              |                |

| VDD         | POWER    | 3.3V power supply. All four pins must be powered.                                             |                |

| HCS         | INPUT    | Host chip select. Data is shifted into HMOSI and out of HMISO when HCS is low                 | Pull-Up        |

| HMISO       | OUTPUT   | Host CPU SPI interface serial data output                                                     | Pull-Down      |

| HMOSI       | INPUT    | Host CPU SPI interface serial data input                                                      | Pull-Down      |

| HSCLK       | INPUT    | Host SPI Clock. Data is shifted into or out of the SPI interface using HSCLK                  | Pull-Down      |

| MCLK        | INPUT    | Master and reference clock for ARINC 429 bus bit timing. 50MHz +/- 0.1%                       |                |

| MRST        | INPUT    | Master Reset to HI-322X Active Low. 225 ns minimum pulse width.                               | Pull-Down      |

| READY       | OUTPUT   | READY goes high when post-RESET initialization is complete                                    |                |

| RUN         | INPUT    | Master enable signal for ARINC 429 transmit schedulers                                        | Pull-Down      |

| SCANEN      | INPUT    | Factory test only. Connect to GND.                                                            | Pull-Down      |

| SCANSHFT    | INPUT    | Factory test only. Connect to GND.                                                            | Pull-Down      |

**NOTE 1:** When not using an external EEPROM, the Mode0, Mode1 and Mode2 pins must be connected to either VDD or GND through a suitable pull-up or pull-down resistor (1K - 50K), depending on the desired power up mode. These pins do not have internal pull-up or pull-down resistors and need to be connected to a known state to prevent possible initialization of an un-intended mode.

NOTE 2: Unused analog receiver inputs (e. g. ARX8P-40, ARX8N-40, etc.) should be left floating.

### **PIN CONFIGURATIONS**

80 - Pin Plastic Quad Flat Pack (PQFP)

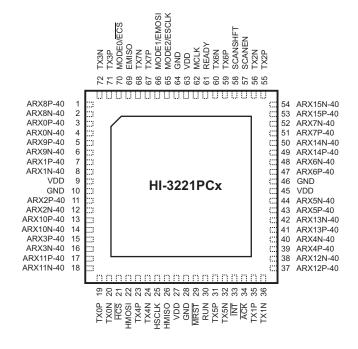

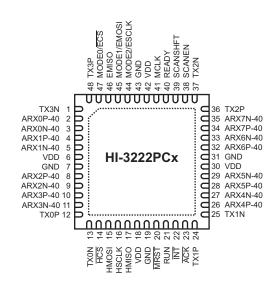

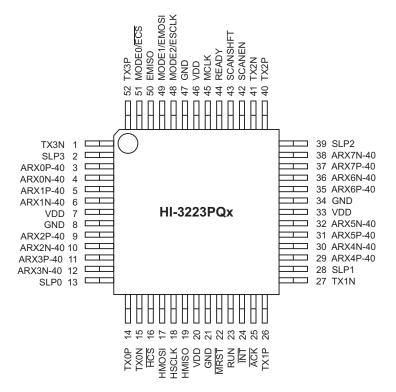

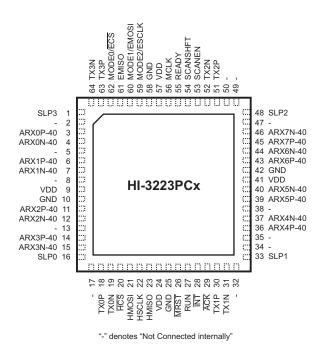

## **PIN CONFIGURATIONS (continued)**

72 - Pin Plastic QFN (Top View)

48 - Pin Plastic QFN (Top View)

52 - Pin Plastic Quad Flat Pack (PQFP)

64 - Pin Plastic QFN (Top View)

## PIN DESCRIPTIONS (HI-3225, HI-3226)

| Signal         | Function       | Description                                                                                                                            | Internal               |

|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------|

|                |                |                                                                                                                                        | Pull-Up/Down           |

| ĀCK            | INPUT          | Interrupt Acknowledge. Active low.                                                                                                     | Pull-Up                |

| ĪNT            | OUTPUT         | Interrupt. Active low, open-drain.                                                                                                     | Pull-Up                |

| RX0N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 0.                                                              | Pull-down              |

| RX0P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 0.                                                              | Pull-down              |

| RX1N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 1.                                                              | Pull-down              |

| RX1P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 1.                                                              | Pull-down              |

| RX2N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 2.                                                              | Pull-down              |

| RX2P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 2.                                                              | Pull-down              |

| RX3N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 3.                                                              | Pull-down              |

| RX3P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 3.                                                              | Pull-down              |

| RX4N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 4.                                                              | Pull-down              |

| RX4P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 4.                                                              | Pull-down              |

| RX5N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 5.                                                              | Pull-down              |

| RX5P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 5.                                                              | Pull-down              |

| RX6N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 6.                                                              | Pull-down              |

| RX6P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 6.                                                              | Pull-down              |

| RX7N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 7.                                                              | Pull-down              |

| RX7P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 7.                                                              | Pull-down              |

| RX8N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 8.                                                              | Pull-down              |

| RX8P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 8.                                                              | Pull-down              |

| RX9N           | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 9.                                                              | Pull-down              |

| RX9P           | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 9.                                                              | Pull-down              |

| RX10N          | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 10.                                                             | Pull-down              |

| RX10P          | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 10.                                                             | Pull-down              |

| RX11N          | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 11.                                                             | Pull-down              |

| RX11P          | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 11.                                                             | Pull-down              |

| RX12N          | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 12.                                                             | Pull-down              |

| RX12P          | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 12.                                                             | Pull-down              |

| RX13N          | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 13.                                                             | Pull-down              |

| RX13P          | INPUT          | ARINC 429 Digital input from line receiver positive signal for channel 13.                                                             | Pull-down              |

| RX14N          | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 14.                                                             | Pull-down              |

| RX14P          | INPUT<br>INPUT | ARINC 429 Digital input from line receiver positive signal for channel 14.                                                             | Pull-down<br>Pull-down |

| RX15N<br>RX15P | INPUT          | ARINC 429 Digital input from line receiver negative signal for channel 15.                                                             | Pull-down              |

| TX0N           | OUTPUT         | ARINC 429 Digital input from line receiver positive signal for channel 15.  ARINC 429 Tx channel 0 negative data output to line driver | Pull-down              |

| TX0P           | OUTPUT         | ARINC 429 Tx channel 0 positive data output to line driver                                                                             |                        |

| TX1N           | OUTPUT         | ARINC 429 Tx channel 1 negative data output to line driver                                                                             |                        |

| TX1P           | OUTPUT         | ARINC 429 Tx channel 1 positive data output to line driver                                                                             |                        |

| TX2N           | OUTPUT         |                                                                                                                                        |                        |

| TX2P           | OUTPUT         | ARINC 429 Tx channel 2 negative data output to line driver  ARINC 429 Tx channel 2 positive data output to line driver                 |                        |

| TX3N           | OUTPUT         | ARINC 429 Tx channel 3 negative data output to line driver                                                                             |                        |

| TX3P           | OUTPUT         | ARINC 429 Tx channel 3 positive data output to line driver                                                                             |                        |

| TX4N           | OUTPUT         | ARINC 429 Tx channel 4 negative data output to line driver                                                                             |                        |

| TX4P           | OUTPUT         | ARINC 429 Tx channel 4 positive data output to line driver                                                                             |                        |

| TX5N           | OUTPUT         | ARINC 429 Tx channel 5 negative data output to line driver                                                                             |                        |

| TX5P           | OUTPUT         | ARINC 429 Tx channel 5 positive data output to line driver                                                                             |                        |

| TX6N           | OUTPUT         | ARINC 429 Tx channel 6 positive data output to line driver                                                                             |                        |

| TX6P           | OUTPUT         | ARINC 429 Tx channel 6 positive data output to line driver                                                                             |                        |

| TX7N           | OUTPUT         | ARINC 429 Tx channel 7 positive data output to line driver                                                                             |                        |

| TX7P           | OUTPUT         | ARINC 429 Tx channel 7 positive data output to line driver                                                                             |                        |

| SLP0           | OUTPUT         | ARINC 429 Tx channel 0 slew rate control (see Tx Control Register) (HI-3225).                                                          |                        |

| SLP1           | OUTPUT         | ARINC 429 Tx channel 1 slew rate control (see Tx Control Register) (HI-3225).                                                          |                        |

| SLP2           | OUTPUT         | ARINC 429 Tx channel 2 slew rate control (see Tx Control Register) (HI-3225).                                                          |                        |

| SLP3           | OUTPUT         | ARINC 429 Tx channel 3 slew rate control (see Tx Control Register) (HI-3225).                                                          |                        |

| SLP4           | OUTPUT         | ARINC 429 Tx channel 4 slew rate control (see Tx Control Register) (HI-3225).                                                          |                        |

| SLP5           | OUTPUT         | ARINC 429 Tx channel 5 slew rate control (see Tx Control Register) (HI-3225).                                                          |                        |

| SLP6           | OUTPUT         | ARINC 429 Tx channel 6 slew rate control (see Tx Control Register) (HI-3225).                                                          |                        |

| SLP7           | OUTPUT         | ARINC 429 Tx channel 7 slew rate control (see Tx Control Register) (HI-3225).                                                          |                        |

## PIN DESCRIPTIONS (HI-3225, HI-3226) continued

| Signal      | Function | Description                                                                                   | Internal       |

|-------------|----------|-----------------------------------------------------------------------------------------------|----------------|

|             |          |                                                                                               | Pull-Up/Down   |

| MODE0/ECS   | I/O      | MODE0 configuration input sampled at reset / SPI chip select output for EEPROM initialization | See Note below |

| EMISO       | INPUT    | SPI serial data input from auto-inialization EEPROM                                           | Pull-Down      |

| MODE1/EMOSI | I/O      | MODE1 configuration input sampled at reset / SPI serial data output for EEPROM initialization | See Note below |

| MODE2/ESCLK | I/O      | MODE2 configuration input sampled at reset / SPI clock for EEPROM auto-initialization         | See Note below |

| GND         | POWER    | Chip 0V supply. All four pins must be connected.                                              |                |

| VDD         | POWER    | 3.3V power supply. All four pins must be powered.                                             |                |

| HCS         | INPUT    | Host chip select. Data is shifted into HMOSI and out of HMISO when HCS is low                 | Pull-Up        |

| HMISO       | OUTPUT   | Host CPU SPI interface serial data output                                                     | Pull-Down      |

| HMOSI       | INPUT    | Host CPU SPI interface serial data input                                                      | Pull-Down      |

| HSCLK       | INPUT    | Host SPI Clock. Data is shifted into or out of the SPI interface using HSCLK                  | Pull-Down      |

| MCLK        | INPUT    | Master and reference clock for ARINC 429 bus bit timing. 50 MHZ +/- 0.1%                      |                |

| MRST        | INPUT    | Master Reset to HI-322X Active Low. 225 ns minimum pulse width.                               | Pull-Down      |

| READY       | OUTPUT   | READY goes high when post-RESET initialization is complete                                    |                |

| RUN         | INPUT    | Master enable signal for ARINC 429 transmit schedulers                                        | Pull-Down      |

| SCANEN      | INPUT    | Factory test only. Connect to GND.                                                            | Pull-Down      |

| SCANSHFT    | INPUT    | Factory test only. Connect to GND.                                                            | Pull-Down      |

**NOTE:** When not using an external EEPROM, the Mode0, Mode1 and Mode2 pins must be connected to either VDD or GND through a suitable pull-up or pull-down resistor (1K - 50K), depending on the desired power up mode. These pins do not have internal pull-up or pull-down resistors and need to be connected to a known state to prevent possible initialization of an un-intended mode.

NOTE 2: Unused digital receiver inputs (e. g. RX15P, RX15N, etc.) should be left floating.

### PIN CONFIGURATIONS

80 - Pin Plastic Quad Flat Pack (PQFP)

72 - Pin Plastic QFN (Top View)

### **APPLICATION OVERVIEW**

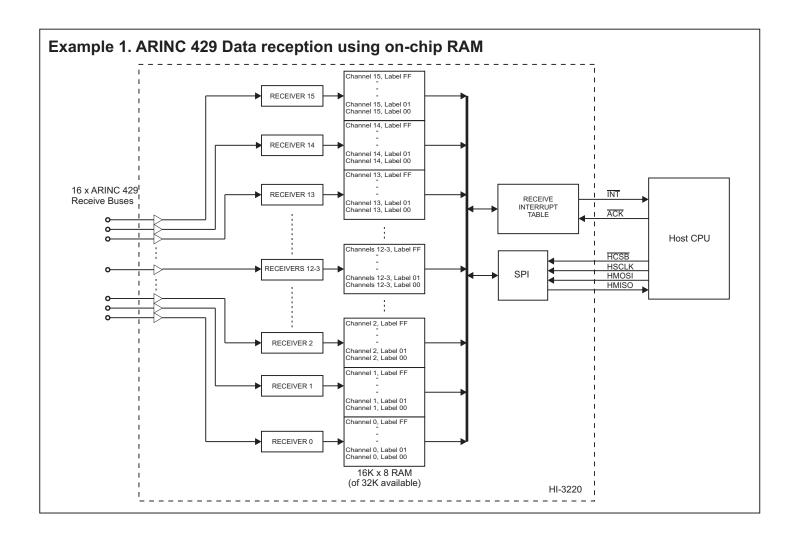

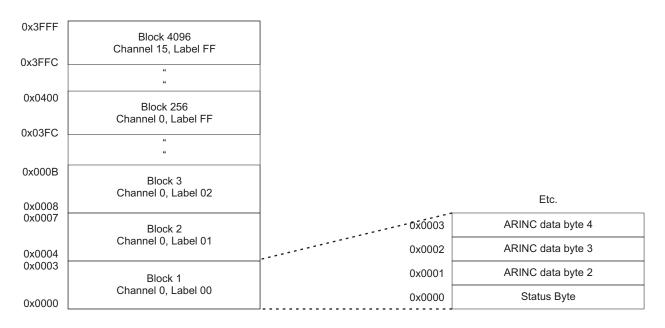

The HI-3220 is a flexible device for managing ARINC 429 communications and data storage in many avionics applications. The device architecture centers around a 32K x 8 static RAM used for data storage, data filtering tables and table-driven transmission schedulers. Once configured, the device can operate autonomously without a host CPU, negating the need for software development or DO-178 certification. Configuration data may be uploaded into the device from an external EEPROM, following system reset.

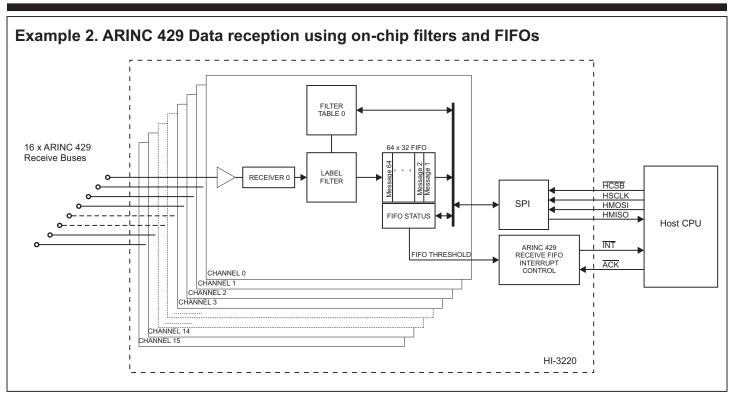

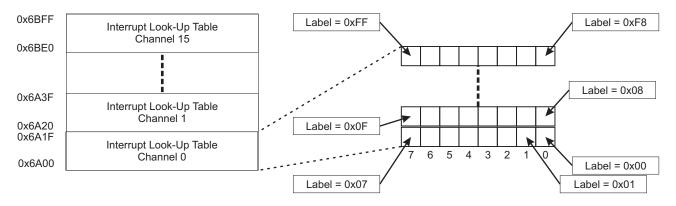

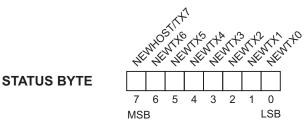

The device supports up to sixteen ARINC 429 receive channels. Analog line receivers are on-chip (HI-3220, HI-3221 and HI-3222), or off-chip (HI-3225 and HI-3226). Received data is stored in on-chip RAM organized by channel number and label. The data table continually updates as new labels arrive. Programmable interrupts and filters alert the host subsystem to labels of interest.

Each ARINC 429 receive channel also includes a 64 message deep FIFO allowing selected label data to be queued for subsequent host access.

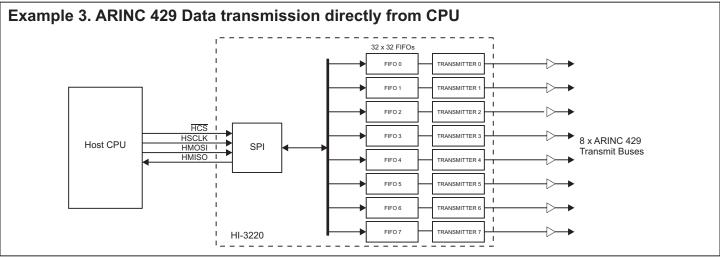

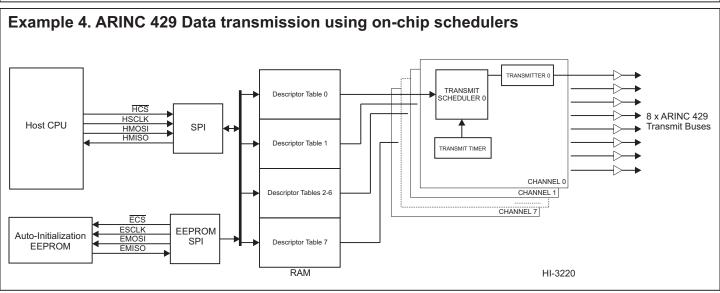

The HI-3220 supports up to eight independent ARINC 429 transmit channels. Transmission may be controlled entirely by an external CPU, or autonomously by programming one or more of the eight on-chip ARINC 429 transmit schedulers. These allow periodic transmission to occur without CPU. Source data for transmission may be selected from RAM based tables of constants and / or from the received channel data. Powerful options exist for constructing ARINC 429 labels as well as controlling their timing and conditional transmission.

Even when running under the control of schedulers, the host CPU may insert new labels for transmission at will.

The following examples show five possible configurations of how the HI-3220 may be used:

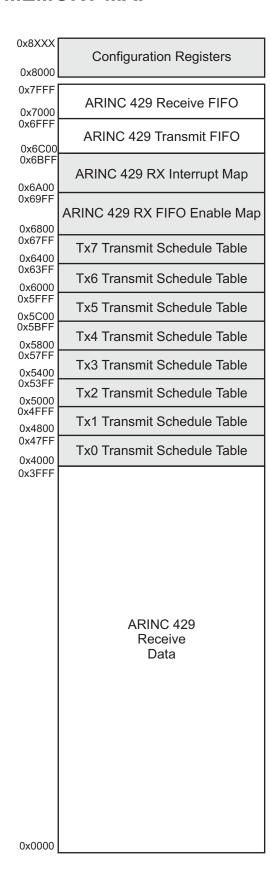

### HI-3220 MEMORY MAP

Shaded Area User - Programmed

Non-shaded Area Data Storage

## HI-3220 REGISTER MAP

| ADDRESS          | R/W    | REGISTER                                                | MNEMONIC     | DESCRIPTION                                                               |

|------------------|--------|---------------------------------------------------------|--------------|---------------------------------------------------------------------------|

| 0x8000           | R/W    | MASTER CONTROL REGISTER                                 | MCR          | HI-3220 global configuration (write address)                              |

| 0x8001           | R      | MASTER CONTROL REGISTER                                 | MCR          | HI-3220 global configuration (read address)                               |

| 0x8002           | R      | MASTER STATUS REGISTER                                  | MSR          | Indicates HI-3220 current status                                          |

| 0x8003           | R      | Not used                                                |              |                                                                           |

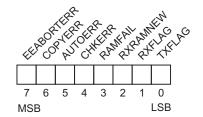

| 0x8004           | R*     | PENDING INTERRUPT REGISTER                              | PIR          | Indicates Interrupt type                                                  |

| 0x8005           | R      | Not used                                                |              |                                                                           |

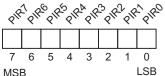

| 0x8006           | R*     | RECEIVE PENDING INTERRUPT LOW                           | RPIRL        | Defines channel(7-0) with pending Interrupt                               |

| 0x8007           | R      | Not used                                                |              |                                                                           |

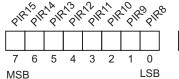

| 0x8008           | R*     | RECEIVE PENDING INTERRUPT HIGH                          | RPIRH        | Defines channel(15-8) with pending Interrupt                              |

| 0x8009           | R      | Not used                                                |              |                                                                           |

| A008x0           | R*     | PENDING INTERRUPT REGISTER                              | PIR          | Indicates Interrupt type                                                  |

| 0x800B           | R*     | RECEIVE PENDING INTERRUPT LOW                           | RPIRL        | Defines channel(7-0) with pending Interrupt                               |

| 0x800C           | R*     | RECEIVE PENDING INTERRUPT HIGH                          | RPIRH        | Defines channel(15-8) with pending Interrupt                              |

| 0x800D           | R      | RECEIVE FIFO THRESHOLD FLAG (LOW)                       | FTFL         | Shows which Rx FIFOs hold > (thresh) words                                |

| 0x800E           | R      | RECEIVE FIFO THRESHOLD FLAG (HIGH)                      | FTFH         | Shows which Rx FIFOs hold > (thresh) words                                |

| 0x800F           | R      | TRANSMITTER FIFO THRESHOLD FLAGS                        | TFR          | Shows which Tx FIFOs hold < (thresh) words                                |

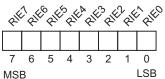

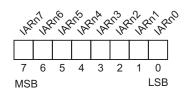

| 0x8010           | R      | RECEIVE INTERRUPT ADDRESS 0                             | IAR0         | ARING 429 Interrupt Vector channel 0                                      |

| 0x8011           | R      | RECEIVE INTERRUPT ADDRESS 1                             | IAR1         | ARING 429 Interrupt Vector channel 1                                      |

| 0x8012           | R      | RECEIVE INTERRUPT ADDRESS 2                             | IAR2         | ARING 429 Interrupt Vector channel 2                                      |

| 0x8013           | R      | RECEIVE INTERRUPT ADDRESS 3                             | IAR3         | ARING 429 Interrupt Vector channel 3                                      |

| 0x8014           | R      | RECEIVE INTERRUPT ADDRESS 4                             | IAR4         | ARING 429 Interrupt Vector channel 4                                      |

| 0x8015           | R      | RECEIVE INTERRUPT ADDRESS 5                             | IAR5         | ARING 429 Interrupt Vector channel 5                                      |

| 0x8016           | R<br>R | RECEIVE INTERRUPT ADDRESS 6                             | IAR6<br>IAR7 | ARING 429 Interrupt Vector channel 6                                      |

| 0x8017<br>0x8018 | R      | RECEIVE INTERRUPT ADDRESS 7 RECEIVE INTERRUPT ADDRESS 8 | IAR7         | ARINC 429 Interrupt Vector channel 7 ARINC 429 Interrupt Vector channel 8 |

| 0x8018           | R      | RECEIVE INTERRUPT ADDRESS 9                             | IAR9         | ARINC 429 Interrupt Vector channel 9                                      |

| 0x8019           | R      | RECEIVE INTERRUPT ADDRESS 10                            | IAR10        | ARINC 429 Interrupt Vector channel 10                                     |

| 0x801B           | R      | RECEIVE INTERRUPT ADDRESS 11                            | IAR11        | ARINC 429 Interrupt Vector channel 11                                     |

| 0x801D           | R      | RECEIVE INTERRUPT ADDRESS 12                            | IAR12        | ARINC 429 Interrupt Vector channel 12                                     |

| 0x801D           | R      | RECEIVE INTERRUPT ADDRESS 13                            | IAR13        | ARINC 429 Interrupt Vector channel 13                                     |

| 0x801E           | R      | RECEIVE INTERRUPT ADDRESS 14                            | IAR14        | ARINC 429 Interrupt Vector channel 14                                     |

| 0x801F           | R      | RECEIVE INTERRUPT ADDRESS 15                            | IAR15        | ARINC 429 Interrupt Vector channel 15                                     |

| 0x8020           | R/W    | RECEIVE CONTROL REGISTER 0                              | RXC0         | Configures ARINC 429 receive channel 0                                    |

| 0x8021           | R/W    | RECEIVE CONTROL REGISTER 1                              | RXC1         | Configures ARINC 429 receive channel 1                                    |

| 0x8022           | R/W    | RECEIVE CONTROL REGISTER 2                              | RXC2         | Configures ARINC 429 receive channel 2                                    |

| 0x8023           | R/W    | RECEIVE CONTROL REGISTER 3                              | RXC3         | Configures ARINC 429 receive channel 3                                    |

| 0x8024           | R/W    | RECEIVE CONTROL REGISTER 4                              | RXC4         | Configures ARINC 429 receive channel 4                                    |

| 0x8025           | R/W    | RECEIVE CONTROL REGISTER 5                              | RXC5         | Configures ARINC 429 receive channel 5                                    |

| 0x8026           | R/W    | RECEIVE CONTROL REGISTER 6                              | RXC6         | Configures ARINC 429 receive channel 6                                    |

| 0x8027           | R/W    | RECEIVE CONTROL REGISTER 7                              | RXC7         | Configures ARINC 429 receive channel 7                                    |

| 0x8028           | R/W    | RECEIVE CONTROL REGISTER 8                              | RXC8         | Configures ARINC 429 receive channel 8                                    |

| 0x8029           | R/W    | RECEIVE CONTROL REGISTER 9                              | RXC9         | Configures ARINC 429 receive channel 9                                    |

| 0x802A           | R/W    | RECEIVE CONTROL REGISTER 10                             | RXC10        | Configures ARINC 429 receive channel 10                                   |

| 0x802B           | R/W    | RECEIVE CONTROL REGISTER 11                             | RXC11        | Configures ARINC 429 receive channel 11                                   |

| 0x802C           | R/W    | RECEIVE CONTROL REGISTER 12                             | RXC12        | Configures ARINC 429 receive channel 12                                   |

| 0x802D           | R/W    | RECEIVE CONTROL REGISTER 13                             | RXC13        | Configures ARINC 429 receive channel 13                                   |

| 0x802E           | R/W    | RECEIVE CONTROL REGISTER 14                             | RXC14        | Configures ARINC 429 receive channel 14                                   |

| 0x802F           | R/W    | RECEIVE CONTROL REGISTER 15                             | RXC15        | Configures ARINC 429 receive channel 15                                   |

Fast Access Registers

Memory mapped register access only

<sup>\*</sup> Register is cleared when read (auto clear)

### HI-3220

| ADDRESS | R/W | REGISTER                             | MNEMONIC | DESCRIPTION                                   |

|---------|-----|--------------------------------------|----------|-----------------------------------------------|

| 0x8030  | R/W | TRANSMIT CONTROL REGISTER 0          | TXC0     | Configures ARINC 429 transmit channel 0       |

| 0x8031  | R/W | TRANSMIT CONTROL REGISTER 1          | TXC1     | Configures ARINC 429 transmit channel 1       |

| 0x8032  | R/W | TRANSMIT CONTROL REGISTER 2          | TXC2     | Configures ARINC 429 transmit channel 2       |

| 0x8033  | R/W | TRANSMIT CONTROL REGISTER 3          | TXC3     | Configures ARINC 429 transmit channel 3       |

| 0x8034  | R/W | TRANSMIT CONTROL REGISTER 4          | TXC4     | Configures ARINC 429 transmit channel 4       |

| 0x8035  | R/W | TRANSMIT CONTROL REGISTER 5          | TXC5     | Configures ARINC 429 transmit channel 5       |

| 0x8036  | R/W | TRANSMIT CONTROL REGISTER 6          | TXC6     | Configures ARINC 429 transmit channel 6       |

| 0x8037  | R/W | TRANSMIT CONTROL REGISTER 7          | TXC7     | Configures ARINC 429 transmit channel 7       |

| 0x8038  | R/W | TRANSMIT REPETITION RATE 0           | TXRR0    | Sets sequence repeat time for ARINC 429 TX0   |

| 0x8039  | R/W | TRANSMIT REPETITION RATE 1           | TXRR1    | Sets sequence repeat time for ARINC 429 TX1   |

| 0x803A  | R/W | TRANSMIT REPETITION RATE 2           | TXRR2    | Sets sequence repeat time for ARINC 429 TX2   |

| 0x803B  | R/W | TRANSMIT REPETITION RATE 3           | TXRR3    | Sets sequence repeat time for ARINC 429 Tx3   |

| 0x803C  | R/W | TRANSMIT REPETITION RATE 4           | TXRR4    | Sets sequence repeat time for ARINC 429 Tx4   |

| 0x803D  | R/W | TRANSMIT REPETITION RATE 5           | TXRR5    | Sets sequence repeat time for ARINC 429 Tx5   |

| 0x803E  | R/W | TRANSMIT REPETITION RATE 6           | TXRR6    | Sets sequence repeat time for ARINC 429 Tx6   |

| 0x803F  | R/W | TRANSMIT REPETITION RATE 7           | TXRR7    | Sets sequence repeat time for ARINC 429 Tx7   |

| 0x8040  | R   | TRANSMIT SEQUENCE POINTER 0          | TXSP0    | Current address of ARINC transmit sequence 0  |

| 0x8041  | R   | TRANSMIT SEQUENCE POINTER 1          | TXSP1    | Current address of ARINC transmit sequence 1  |

| 0x8042  | R   | TRANSMIT SEQUENCE POINTER 2          | TXSP2    | Current address of ARINC transmit sequence 2  |

| 0x8043  | R   | TRANSMIT SEQUENCE POINTER 3          | TXSP3    | Current address of ARINC transmit sequence 3  |

| 0x8044  | R   | TRANSMIT SEQUENCE POINTER 4          | TXSP4    | Current address of ARINC transmit sequence 4  |

| 0x8045  | R   | TRANSMIT SEQUENCE POINTER 5          | TXSP5    | Current address of ARINC transmit sequence 5  |

| 0x8046  | R   | TRANSMIT SEQUENCE POINTER 6          | TXSP6    | Current address of ARINC transmit sequence 6  |

| 0x8047  | R   | TRANSMIT SEQUENCE POINTER 7          | TXSP7    | Current address of ARINC transmit sequence 7  |

| 0x8048  | R   | Not used                             |          | ·                                             |

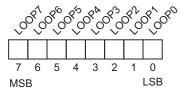

| 0x8049  | R/W | LOOPBACK                             | LOOP     | Sets Loopback channels                        |

| 0x804A  | R/W | PENDING INTERRUPT ENABLE REGISTER    | PIER     | Enables Interrupts on INT pin                 |

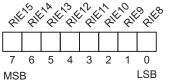

| 0x804B  | R/W | RECEIVE INTERRUPT ENABLE (LOW)       | RIEL     | Enables Interrupts (channels 7-0)             |

| 0x804C  | R/W | RECEIVE INTERRUPT ENABLE (HIGH)      | RIEH     | Enables Interrupts (channels 15-8)            |

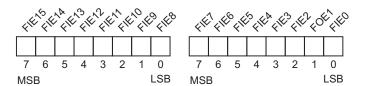

| 0x804D  | R/W | RECEIVE FIFO INTERRUPT ENABLE (LOW)  | FIEL     | Enables Receive Interrupts (channels 7-0)     |

| 0x804E  | R/W | RECEIVE FIFO INTERRUPT ENABLE (HIGH) | FIEH     | Enables Receive Interrupts (channels 15-8)    |

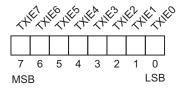

| 0x804F  | R/W | TRANSMIT FIFO INTERRUPT ENABLE       | TFIE     | Enables Transmit Interrupts                   |

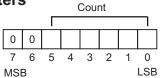

| 0x8050  | R/W | RECEIVE FIFO THRESHOLD VALUE 0       | FTV0     | Sets flag value for ARINC 429 Receive FIFO 0  |

| 0x8051  | R/W | RECEIVE FIFO THRESHOLD VALUE 1       | FTV1     | Sets flag value for ARINC 429 Receive FIFO 1  |

| 0x8052  | R/W | RECEIVE FIFO THRESHOLD VALUE 2       | FTV2     | Sets flag value for ARINC 429 Receive FIFO 2  |

| 0x8053  | R/W | RECEIVE FIFO THRESHOLD VALUE 3       | FTV3     | Sets flag value for ARINC 429 Receive FIFO 3  |

| 0x8054  | R/W | RECEIVE FIFO THRESHOLD VALUE 4       | FTV4     | Sets flag value for ARINC 429 Receive FIFO 4  |

| 0x8055  | R/W | RECEIVE FIFO THRESHOLD VALUE 5       | FTV5     | Sets flag value for ARINC 429 Receive FIFO 5  |

| 0x8056  | R/W | RECEIVE FIFO THRESHOLD VALUE 6       | FTV6     | Sets flag value for ARINC 429 Receive FIFO 6  |

| 0x8057  | R/W | RECEIVE FIFO THRESHOLD VALUE 7       | FTV7     | Sets flag value for ARINC 429 Receive FIFO 7  |

| 0x8058  | R/W | RECEIVE FIFO THRESHOLD VALUE 8       | FTV8     | Sets flag value for ARINC 429 Receive FIFO 8  |

| 0x8059  | R/W | RECEIVE FIFO THRESHOLD VALUE 9       | FTV9     | Sets flag value for ARINC 429 Receive FIFO 9  |

| 0x805A  | R/W | RECEIVE FIFO THRESHOLD VALUE 10      | FTV10    | Sets flag value for ARINC 429 Receive FIFO 10 |

| 0x805B  | R/W | RECEIVE FIFO THRESHOLD VALUE 11      | FTV11    | Sets flag value for ARINC 429 Receive FIFO 11 |

| 0x805C  | R/W | RECEIVE FIFO THRESHOLD VALUE 12      | FTV12    | Sets flag value for ARINC 429 Receive FIFO 12 |

| 0x805D  | R/W | RECEIVE FIFO THRESHOLD VALUE 13      | FTV13    | Sets flag value for ARINC 429 Receive FIFO 13 |

| 0x805E  | R/W | RECEIVE FIFO THRESHOLD VALUE 14      | FTV14    | Sets flag value for ARINC 429 Receive FIFO 14 |

| 0x805F  | R/W | RECEIVE FIFO THRESHOLD VALUE 15      | FTV15    | Sets flag value for ARINC 429 Receive FIFO 15 |

### HI-3220

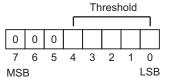

| 0x8060         R/W         TRANSMIT FIFO THRESHOLD VALUE 0         TFTV0         Sets flag value for ARINC 429 Transmit FIFO 0x8061           0x8061         R/W         TRANSMIT FIFO THRESHOLD VALUE 2         TFTV1         Sets flag value for ARINC 429 Transmit FIFO 0x8062         R/W         TRANSMIT FIFO THRESHOLD VALUE 2         TFTV2         Sets flag value for ARINC 429 Transmit FIFO 0x8063         R/W         TRANSMIT FIFO THRESHOLD VALUE 4         TFTV3         Sets flag value for ARINC 429 Transmit FIFO 0x8064         R/W         TRANSMIT FIFO THRESHOLD VALUE 4         TFTV4         Sets flag value for ARINC 429 Transmit FIFO 0x8066         R/W         TRANSMIT FIFO THRESHOLD VALUE 6         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 0x8066         R/W         TRANSMIT FIFO THRESHOLD VALUE 6         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 0x8066         R/W         TRANSMIT FIFO THRESHOLD VALUE 6         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 0x8066         R/W         TRANSMIT FIFO THRESHOLD VALUE 6         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 0x8066         R/W         RXFIFO COUNT 1         RFC0         Current FIFO message count Receiver 3         Sets flag value for ARINC 429 Transmit FIFO 0x8066         R/W         RXFIFO COUNT 1         RFC0         Current FIFO message count Receiver 1         RRC2                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ADDRESS | R/W | REGISTER                         | MNEMONIC | DESCRIPTION                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|----------------------------------|----------|-----------------------------------------------|

| 0x8061         R/W         TRANSMIT FIFO THRESHOLD VALUE 1         TETV1         Sets flag value for ARINC 429 Transmit FIFO 2x8062           0x8063         R/W         TRANSMIT FIFO THRESHOLD VALUE 3         TETV2         Sets flag value for ARINC 429 Transmit FIFO 2x8063           0x8064         R/W         TRANSMIT FIFO THRESHOLD VALUE 4         TETV4         Sets flag value for ARINC 429 Transmit FIFO 2x8066           0x8065         R/W         TRANSMIT FIFO THRESHOLD VALUE 5         TETV5         Sets flag value for ARINC 429 Transmit FIFO 2x8066           0x8066         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TETV7         Sets flag value for ARINC 429 Transmit FIFO 2x8066           0x8067         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TETV7         Sets flag value for ARINC 429 Transmit FIFO 2x8066           0x8068         R/W         TRANSMIT FIFO COUNT 1         RFC0         Current FIFO message count Receiver 0           0x8069         R/W         RX FIFO COUNT 1         RFC1         Current FIFO message count Receiver 1           0x8060         R/W         RX FIFO COUNT 3         RFC3         Current FIFO message count Receiver 2           0x8060         R/W         RX FIFO COUNT 4         RFC4         Current FIFO message count Receiver 4           0x8060         R/W         RX FIFO COUNT 5         RFC5         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x8060  | R/W | TRANSMIT FIFO THRESHOLD VALUE 0  | TFTV0    | Sets flag value for ARINC 429 Transmit FIFO 0 |

| 0x8062         R/W         TRANSMIT FIFO THRESHOLD VALUE 2         TFTV2         Sets flag value for ARINC 429 Transmit FIFO 2           0x8064         R/W         TRANSMIT FIFO THRESHOLD VALUE 4         TFTV3         Sets flag value for ARINC 429 Transmit FIFO 2           0x8065         R/W         TRANSMIT FIFO THRESHOLD VALUE 5         TFTV5         Sets flag value for ARINC 429 Transmit FIFO 2           0x8066         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 2           0x8067         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 2           0x8068         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 2           0x8068         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 2           0x8068         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 2           0x8068         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 2           0x8068         R/W         RX FIFO COUNT 1         RFC1         Current FIFO message count Receiver 1           0x8068         R/W         RX FIFO COUNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |     |                                  |          | _                                             |

| 0x8063         RW         TRANSMIT FIFO THRESHOLD VALUE 3         TFTV3         Sets flag value for ARINC 429 Transmit FIFO 2           0x8066         RW         TRANSMIT FIFO THRESHOLD VALUE 5         TFTV4         Sets flag value for ARINC 429 Transmit FIFO 2           0x8066         RW         TRANSMIT FIFO THRESHOLD VALUE 6         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 1           0x8067         RW         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV7         Sets flag value for ARINC 429 Transmit FIFO 1           0x8068         RW         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV7         Sets flag value for ARINC 429 Transmit FIFO 1           0x8068         RW         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV7         Sets flag value for ARINC 429 Transmit FIFO 1           0x8069         RW         TRASHIT FIFO COUNT 1         RFC0         Current FIFO message count Receiver 0           0x8069         RW         RX FIFO COUNT 1         RFC1         Current FIFO message count Receiver 2           0x8060         RW         RX FIFO COUNT 3         RFC3         Current FIFO message count Receiver 3           0x8060         RW         RX FIFO COUNT 5         RFC4         Current FIFO message count Receiver 6           0x806E         RW         RX FIFO COUNT 7         RFC6         Current FIFO message count Receiver 1 </td <td></td> <td></td> <td></td> <td></td> <td>_</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |     |                                  |          | _                                             |

| 0x8064         R/W         TRANSMIT FIFO THRESHOLD VALUE 4         TFTV4         Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC 429 Transmit FIFO J. Sets flag value for ARINC |         |     |                                  |          | <u> </u>                                      |

| 0x8065         R/W         TRANSMIT FIFO THRESHOLD VALUE 5         TFTV5         Sets flag value for ARINC 429 Transmit FIFO 16 0x8067           0x8067         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 1 0x8068         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV7         Sets flag value for ARINC 429 Transmit FIFO 1 0x8068         R/W         RX FIFO COUNT 0         RFC0         Current FIFO message count Receiver 0 0x8069         R/W         RX FIFO COUNT 1         RFC1         Current FIFO message count Receiver 1 0x8068         R/W         RX FIFO COUNT 2         RFC2         Current FIFO message count Receiver 2 0x8068         R/W         RX FIFO COUNT 3         RFC3         Current FIFO message count Receiver 3 0x806C         R/W         RX FIFO COUNT 4         RFC4         Current FIFO message count Receiver 3 0x806C         R/W         RX FIFO COUNT 5         RFC5         Current FIFO message count Receiver 5 0x806E         R/W         RX FIFO COUNT 6         RFC6         Current FIFO message count Receiver 5 0x806E         R/W         RX FIFO COUNT 7         RFC7         Current FIFO message count Receiver 6 0x806F         R/W         RX FIFO COUNT 7         RFC7         Current FIFO message count Receiver 6 0x8071         R/W         RX FIFO COUNT 8         RFC8         Current FIFO message count Receiver 1 0x8072         R/W         RX FIFO COUNT 9         RFC9         Current FI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |     |                                  |          | •                                             |

| 0x8066         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV6         Sets flag value for ARINC 429 Transmit FIFO 6           0x8068         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV7         Sets flag value for ARINC 429 Transmit FIFO 6           0x8068         R/W         RX FIFO COUNT 1         RFC0         Current FIFO message count Receiver 1           0x8068         R/W         RX FIFO COUNT 2         RFC1         Current FIFO message count Receiver 1           0x806B         R/W         RX FIFO COUNT 3         RFC3         Current FIFO message count Receiver 2           0x806B         R/W         RX FIFO COUNT 4         RFC4         Current FIFO message count Receiver 3           0x806C         R/W         RX FIFO COUNT 5         RFC6         Current FIFO message count Receiver 4           0x806D         R/W         RX FIFO COUNT 6         RFC6         Current FIFO message count Receiver 5           0x806F         R/W         RX FIFO COUNT 7         RFC7         Current FIFO message count Receiver 6           0x8070         R/W         RX FIFO COUNT 9         RFC8         Current FIFO message count Receiver 7           0x8071         R/W         RX FIFO COUNT 10         RFC10         Current FIFO message count Receiver 9           0x8073         R/W         RX FIFO COUN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |     |                                  |          | <u> </u>                                      |

| 0x8067         R/W         TRANSMIT FIFO THRESHOLD VALUE 7         TFTV7         Sets flag value for ARINC 429 Transmit FIFO 2 0x8068         R/W         RX FIFO COUNT 1         RFC0         Current FIFO message count Receiver 0 0x8068         R/W         RX FIFO COUNT 1         RFC1         Current FIFO message count Receiver 1 0x806A         R/W         RX FIFO COUNT 2         RFC2         Current FIFO message count Receiver 2 0x806B         R/W         RX FIFO COUNT 3         RFC3         Current FIFO message count Receiver 3 0x806C         R/W         RX FIFO COUNT 4         RFC4         Current FIFO message count Receiver 4 0x806D         R/W         RX FIFO COUNT 5         RFC5         Current FIFO message count Receiver 4 0x806D         R/W         RX FIFO COUNT 5         RFC6         Current FIFO message count Receiver 5 0x806E         R/W         RX FIFO COUNT 6         RFC6         Current FIFO message count Receiver 6 0x806F         R/W         RX FIFO COUNT 7 RFC7         Current FIFO message count Receiver 7 0x8070         R/W         RX FIFO COUNT 8 RFC8         Current FIFO message count Receiver 7 0x8070         R/W         RX FIFO COUNT 9 RFC9         Current FIFO message count Receiver 9 0x8071         RX FIFO COUNT 10 RFC10         Current FIFO message count Receiver 10 0x8073         R/W         RX FIFO COUNT 11 RFC11         RFC11         Current FIFO message count Receiver 11 0x8074         RX FIFO COUNT 12 RFC11         Current FIFO message count Receiver 12 0x8075         R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |     |                                  |          | _                                             |

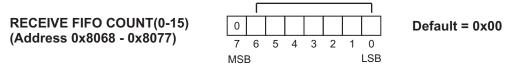

| 0x8068         R/W         RX FIFO COUNT 0         RFC0         Current FIFO message count Receiver 0           0x8069         R/W         RX FIFO COUNT 1         RFC1         Current FIFO message count Receiver 1           0x806A         R/W         RX FIFO COUNT 2         RFC2         Current FIFO message count Receiver 2           0x806B         R/W         RX FIFO COUNT 3         RFC3         Current FIFO message count Receiver 3           0x806C         R/W         RX FIFO COUNT 4         RFC4         Current FIFO message count Receiver 4           0x806D         R/W         RX FIFO COUNT 5         RFC5         Current FIFO message count Receiver 5           0x806E         R/W         RX FIFO COUNT 6         RFC6         Current FIFO message count Receiver 6           0x806F         R/W         RX FIFO COUNT 7         RFC7         Current FIFO message count Receiver 7           0x8071         R/W         RX FIFO COUNT 9         RFC8         Current FIFO message count Receiver 9           0x8073         R/W         RX FIFO COUNT 10         RFC10         Current FIFO message count Receiver 10           0x8073         R/W         RX FIFO COUNT 11         RFC11         Current FIFO message count Receiver 11           0x8074         R/W         RX FIFO COUNT 12         RFC12         C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |     |                                  |          | _                                             |

| 0x8069         R/W         RX FIFO COUNT 1         RFC1         Current FIFO message count Receiver 1           0x806A         R/W         RX FIFO COUNT 2         RFC2         Current FIFO message count Receiver 2           0x806B         R/W         RX FIFO COUNT 3         RFC3         Current FIFO message count Receiver 4           0x806C         R/W         RX FIFO COUNT 4         RFC4         Current FIFO message count Receiver 4           0x806D         R/W         RX FIFO COUNT 5         RFC5         Current FIFO message count Receiver 5           0x806E         R/W         RX FIFO COUNT 6         RFC6         Current FIFO message count Receiver 6           0x807D         R/W         RX FIFO COUNT 7         RFC7         Current FIFO message count Receiver 6           0x8071         R/W         RX FIFO COUNT 8         RFC9         Current FIFO message count Receiver 7           0x8072         R/W         RX FIFO COUNT 10         RFC9         Current FIFO message count Receiver 9           0x8073         R/W         RX FIFO COUNT 11         RFC11         Current FIFO message count Receiver 10           0x8073         R/W         RX FIFO COUNT 12         RFC12         Current FIFO message count Receiver 11           0x8074         R/W         RX FIFO COUNT 13         RFC13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |     |                                  |          | <u> </u>                                      |

| 0x806A         R/W         RX FIFO COUNT 2         RFC2         Current FIFO message count Receiver 2           0x806B         R/W         RX FIFO COUNT 3         RFC3         Current FIFO message count Receiver 4           0x806D         R/W         RX FIFO COUNT 5         RFC4         Current FIFO message count Receiver 4           0x806E         R/W         RX FIFO COUNT 6         RFC5         Current FIFO message count Receiver 6           0x806F         R/W         RX FIFO COUNT 7         RFC7         Current FIFO message count Receiver 7           0x807D         R/W         RX FIFO COUNT 8         RFC8         Current FIFO message count Receiver 7           0x8071         R/W         RX FIFO COUNT 9         RFC9         Current FIFO message count Receiver 8           0x8071         R/W         RX FIFO COUNT 10         RFC10         Current FIFO message count Receiver 9           0x8073         R/W         RX FIFO COUNT 11         RFC11         Current FIFO message count Receiver 10           0x8073         R/W         RX FIFO COUNT 12         RFC12         Current FIFO message count Receiver 11           0x8074         R/W         RX FIFO COUNT 13         RFC13         Current FIFO message count Receiver 13           0x8075         R/W         RX FIFO COUNT 14         RFC14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |     |                                  |          | <u> </u>                                      |

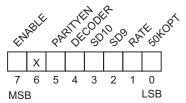

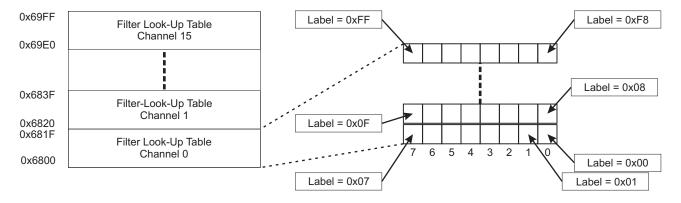

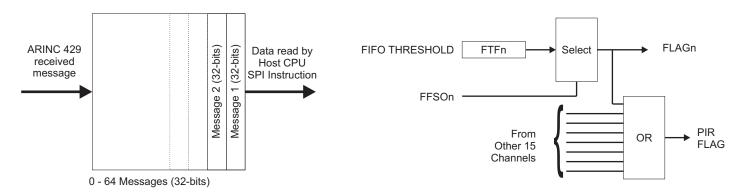

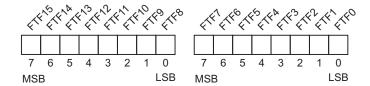

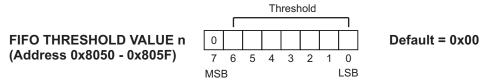

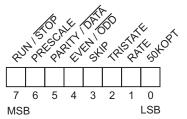

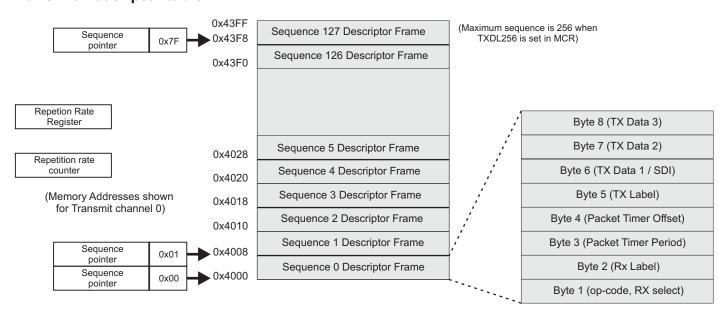

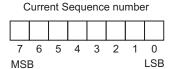

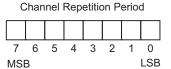

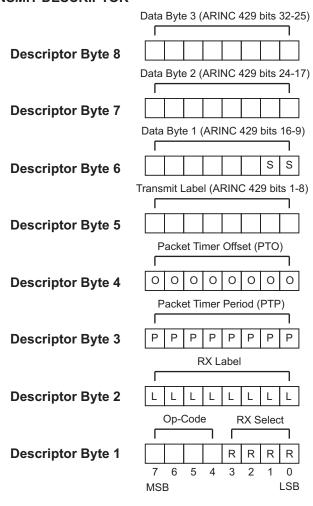

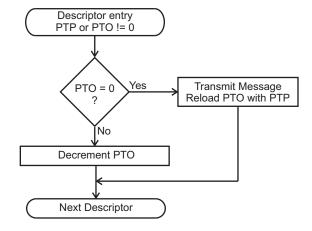

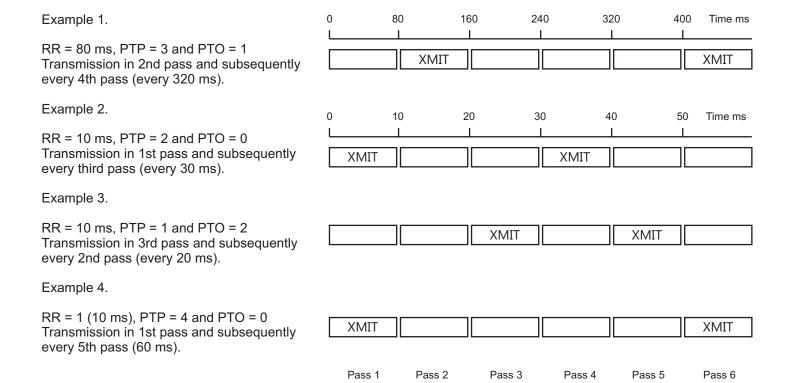

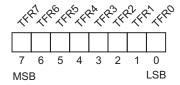

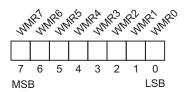

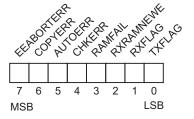

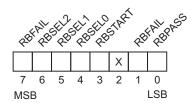

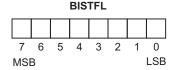

| 0x806BR/WRX FIFO COUNT 3RFC3Current FIFO message count Receiver 30x806CR/WRX FIFO COUNT 4RFC4Current FIFO message count Receiver 40x806DR/WRX FIFO COUNT 5RFC5Current FIFO message count Receiver 50x806ER/WRX FIFO COUNT 6RFC6Current FIFO message count Receiver 60x806FR/WRX FIFO COUNT 7RFC7Current FIFO message count Receiver 70x8070R/WRX FIFO COUNT 8RFC8Current FIFO message count Receiver 80x8071R/WRX FIFO COUNT 9RFC9Current FIFO message count Receiver 90x8072R/WRX FIFO COUNT 10RFC10Current FIFO message count Receiver 100x8073R/WRX FIFO COUNT 11RFC11Current FIFO message count Receiver 110x8074R/WRX FIFO COUNT 12RFC12Current FIFO message count Receiver 120x8075R/WRX FIFO COUNT 13RFC13Current FIFO message count Receiver 130x8076R/WRX FIFO COUNT 14RFC14Current FIFO message count Receiver 130x8077R/WRX FIFO COUNT 15RFC15Current FIFO message count Receiver 150x8078RBIST FAIL ADDRESS [7:0]BISTFBISTFBISTF0x8079RBIST FAIL ADDRESS [15:8]BISTFAuto-initialization fail address (low-byte)0x807DRAUTO-INIT FAIL LS ADDRESS [15:8]AIFHAuto-initialization fail address (low-byte)0x807DRWATCHDOG TIMER REGISTER [7:0]WTRDefines w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |     |                                  |          |                                               |